DATA SHEET

Download Datasheet - I3C Protocol Validation Suite Specifications

Download Datasheet - I3C Protocol Validation Suite Specifications

Download Datasheet - I3C Protocol Validation Suite Specifications

Please enter your details, you will receive an immediate automated email with our I3C Protocol Validation Suite Datasheet.

Product Details

- Overview

- Functional Coverage

- Parametric Coverage

- Features

- FAQ

Overview

MIPI I3C® is a scalable, medium-speed, utility, and control bus interface for connecting peripherals to an application processor, streamlining integration, and improving cost efficiencies. It gives developers unprecedented opportunities to craft innovative designs for any mobile product—from smartphones to wearables, to systems in automobiles.

As a part of product validation, it’s important to validate the product’s conformance against the protocol specification to ensure the interoperability of the product. As the complexity of the protocol and product increases, the validation time of the protocol interfaces also increases which in turn reduces the RTM. Performing the protocol conformance testing in the traditional way needs a lot of time and effort.

Soliton’s I3C Validation Suite is an off-the-shelf validation tool using NI’s PXI platform, which helps to validate the devices’ compliance with the timing and electrical specifications of the MIPI I3C protocol. The tool can also validate the device’s tolerance to and recovery from a variety of I3C faults & exceptions and provides a comprehensive set of reports. Users have claimed that using this automated solution for I3C Validation has brought down the test time/ validation time from a few weeks to a couple of days.

Functional Coverage

MODES

- Legacy I2C Mode (5 MHz)

- I3C SDR mode (15 MHz)

- I3C HDR-DDR mode (15 MHz)

- I3C SDR Multilane Mode (15 MHz)

FUNCTIONAL TESTS

- Register Write (Legacy I2C /SDR/HDR)

- Register Read (Legacy I2C /SDR/HDR)

- Write N Bytes (Legacy I2C /SDR/HDR)

- Read N Bytes (Legacy I2C /SDR/HDR)

- Write N – Read N Bytes (Combined Format) (Legacy I2C /SDR/HDR)

- Hot-Join Functional Test

- IBI Functional Test

- IBI Interrupt Spacing Tests

- Clock Stalling

- Conformance Test Suite (CTS)

DEVICE MODES

- Target (Slave)

- Control (Master)

PROTOCOL FEATURES

- Dynamic/Static Addressing

- Direct and Broadcast CCC Commands

- START / STOP Conditions

- Address Header and Transition Bit

- HDR DDR Restart and Exit Patterns

- Target Reset Pattern

- Group Target Addressing

FAULT TESTS

- Induce SDR Errors (S0-S5) & (CE0-CE2)

- Induce HDR DDR Errors

- Skip Start / Stop / Repeated Start

- Skip HDR Restart / HDR Exit

- Add clocks from address/data bytes

- Skip clocks from address/data bytes

- Induce Parity/Preamble Errors

- Induce Errors in CRC5 Calculation

- Any custom faults in SDR/ HDR DDR transactions and can check if the Target is able to recover from the faults.

Parametric Coverage

I2C Legacy Timing Parameters

- fSCL SCL Clock Frequency

- tSU_STA Setup time for Repeated Start

- tHD_STA Hold time for a (Repeated) start

- tLOW SCL Clock Low Period

- tHIGH SCL Clock High Period

- tSU_DAT Data Setup Time

- tHD_DAT Data Hold Time

- trCL SCL signal Rise time

- tfCL SCL signal Fall time

- trDA SDA signal Rise time

- tfDA SDA signal Fall time

- tSU_STO Setup time for Stop

- tBUF Bus Free time between a Stop and a Start

- tSPIKE Pulse width of spikes to supress

- tDIG_H Digital SCL Clock High Period

- tDIG_L Digital SCL Clock Low Period

- tTIMEOUT – Detect Clock Input Low Time

- tDOUT – SCL Falling Clock In to valid SDA Output Time

Electrical IO Parameters

- VIL Low-Level Input Voltage

- VIH High-Level Input Voltage

- Vhys Schmitt Trigger Inputs Hysteresis

- VOL Output Low Level

- VOH Output High Level

I3C Push-Pull Timing Parameters

- fSCL SCL Clock Frequency

- tLOW_PP SCL Clock Low Period

- tHIGH_PP SCL Clock High Period

- tSCO Clock into Data out for responder

- tCR SCL Clock Rise Time

- tCF SCL Clock Fall Time

- tHD_PP SDA signal Data Hold in Push-pull mode

- tSU_PP SDA signal Data Setup in Push-pull mode

- tCASr Clock after Repeated start condition

- tCBSr Clock before Repeated start condition

- tDIG_H Digital SCL Clock High Period

- tDIG_L Digital SCL Clock Low Period

Open-Drain Timing Parameters

- tLOW_OD Low period of SCL clock

- tHIGH_OD High period of SCL clock

- tfDA_OD Fall time of SDA signal

- tSU_OD Data setup time during open-drain mode

- tCAS Clock after start condition

- tCBP Clock before stop condition

- tAVAL Bus Available Condition

- tIDLE Bus Idle Condition

- tDIG_H Digital SCL Clock High Period

- tDIG_OD_L Digital SCL Clock Low Period

Other Parameters

- tDOFFS -SCL Rising Clock In to Target SDA Output Off

- tDOFFM – SCL Rising Clock In to Master SDA Output Off

- tCL_r_DAT_f – SCL Rising Clock In to Master Driving Data Signal Low

tIBI_ISSUE – Time to issue IBI after an event is detected when Bus is available - tCLR_I3C_CMD_ Delay – Time from Clear Register Status to any I3C operation with Start condition to avoid false IBI generation

- tDEVCTRLCCC_ DELAY_PEC_DIS – DEVCTRL CCC Followed by DEVCTRL CCC or Register Read/Write Command Delay

- tWR_RD_DELAY _PEC_EN – Register Write Command Followed by Register Read Command Delay in PEC Enabled Mode

- tI3C_CCC_Update _Delay – RSTDAA CCC or ENEC CCC or DISEC CCC to any other CCC or Read/Write Command Delay

- tCCC_Delay – Any CCC followed by RSTDAA CCC delay

Features

Features of I3C Protocol Validation

- ISO 9001 Certified Product

- Simple, Flexible, Modular, and Light Bench Setup

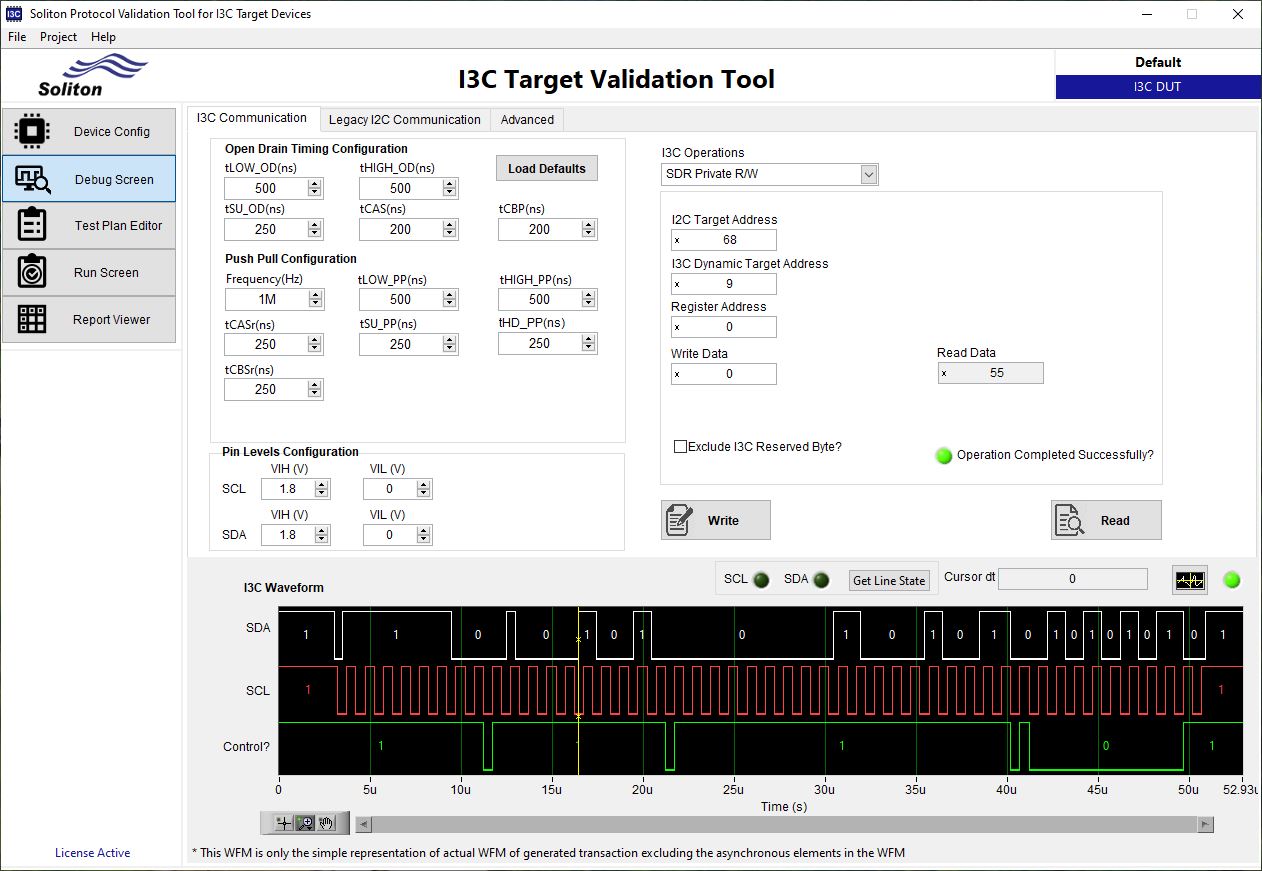

- Easy to use I3C Protocol Exerciser and Debugger to perform various I3C transactions with controllable timings/voltage levels

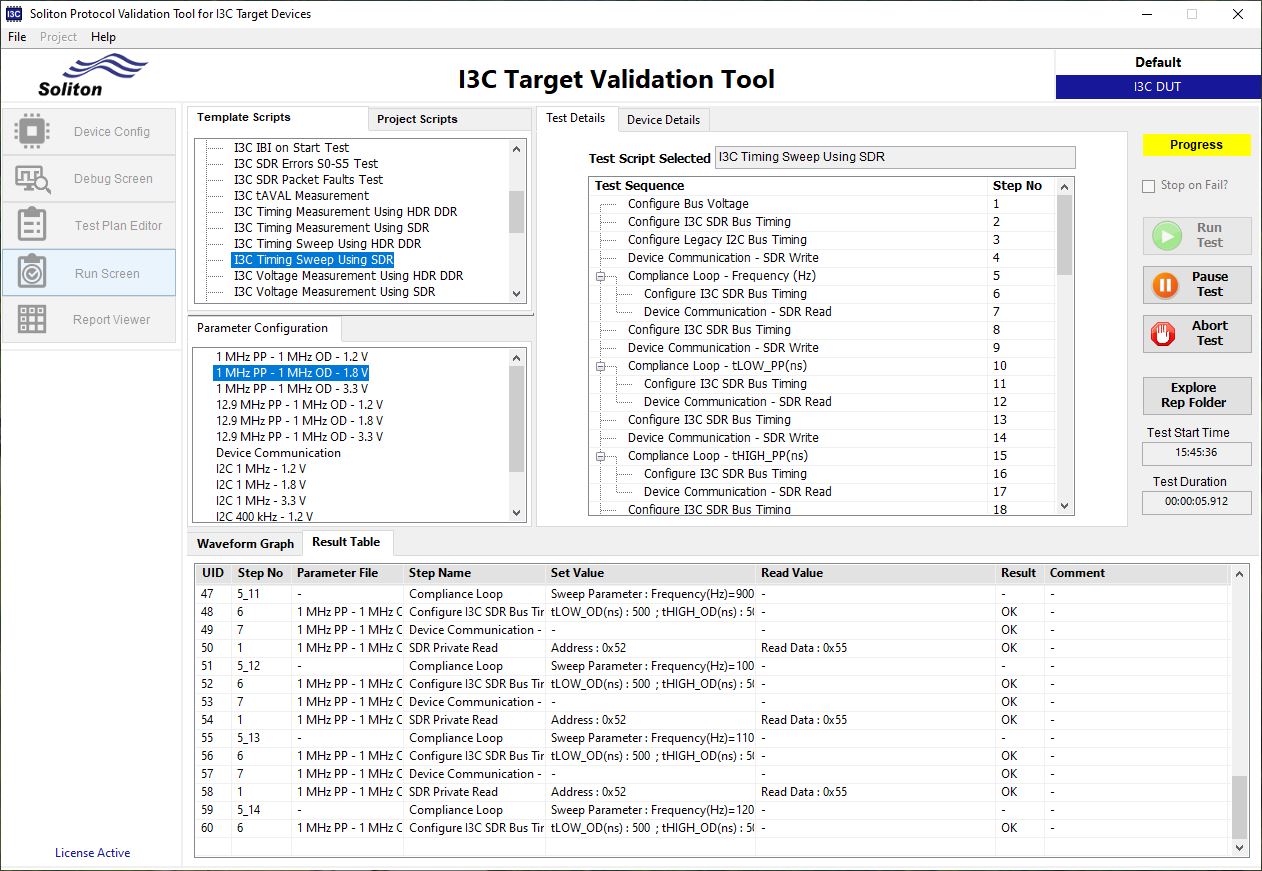

- Protocol compliance testing with zero coding

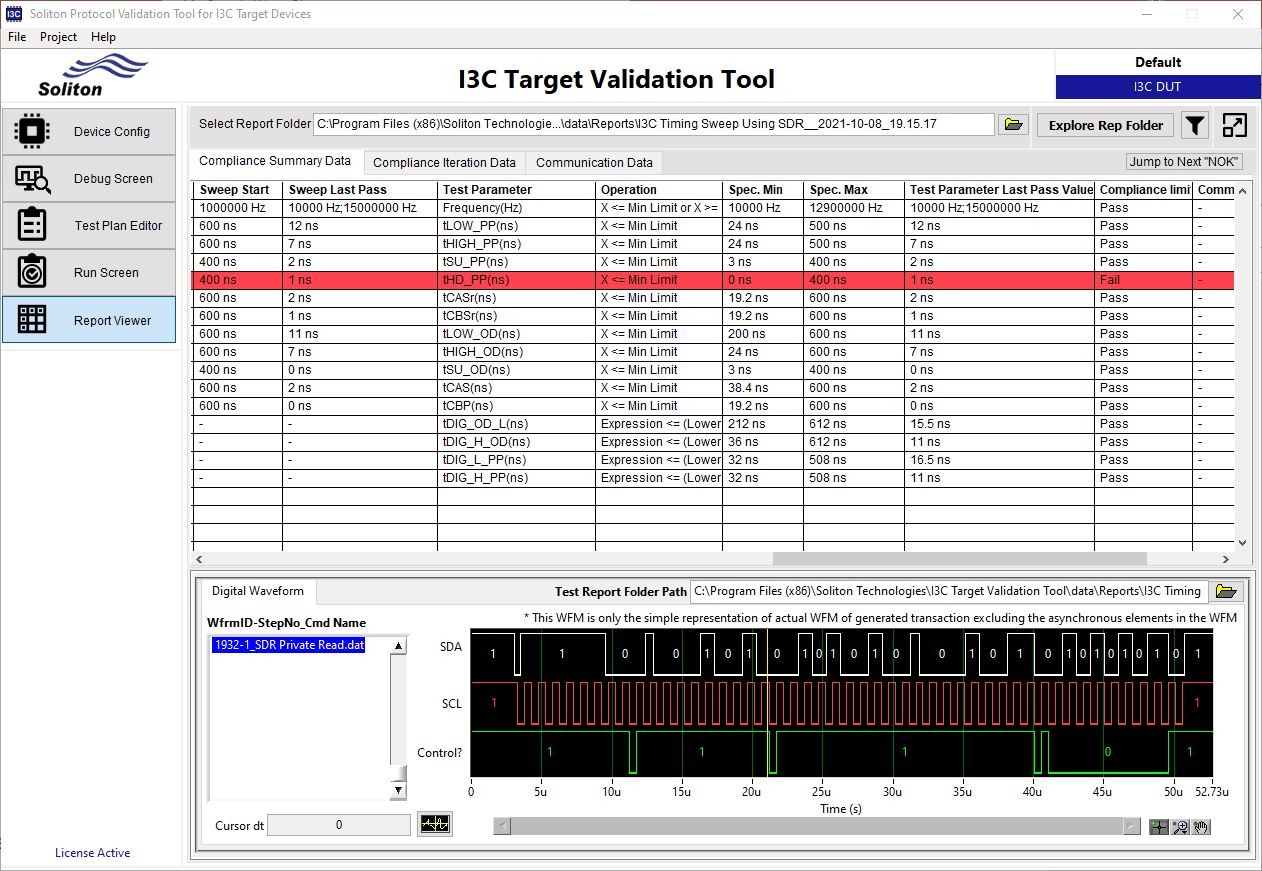

- Comprehensive reporting feature to report the test pass/fail reports

- Generates Full Compliance reports in less than 2 hours

- Reproduce failure cases in a few clicks

- Easy to build and test custom device-specific tests

- Automation Capability (DLLs/APIs) from external programming environment/automation frameworks like LabVIEW, C#, Python, TestStand, etc

- Leverage Soliton’s experience in protocol validation and debugging.

FAQ

What kind of engagement models are offered for I3C Validation

We offer 2 engagement models. In the First mode, the user can purchase a license of the I3C Validation Suite and do the validation in-house. In the second mode, the user can send us 3 DUT's, we will do the I3C validation and send the test reports in 3 working days

How is this product different from existing Protocol Exercisers, Debugger or Analyzers?

This product is mainly used for performing functional and electrical compliance validation of the I3C devices (post-silicon validation) whereas the other existing protocol exercisers, debuggers, or analyzers are used for performing basic functional tests during the device bring up

Can't I build a home-grown solution instead?

While this is certainly an option, we expect that it will take a highly experienced automation engineer between 3-6 months to create the first version of a similar tool. To create a robust and flexible tool takes experience, and we have been improving this tool over the last 3 years since its release. We believe it is worth the cost to skip the learning curve and avail of our comprehensive report or validation suite.

What else can I do with NI's PXI chassis/modules?

The PXIe-657x module is a general-purpose programmable pattern generator and acquisition device with deep memory. It can be used for other protocol validation tools from us. Also, it can be programmed using LabVIEW or other programming languages to emulate any synchronous digital protocol. NI’s PXI chassis supports high bandwidth and synchronization-friendly control and reads back from a huge variety of digital, analog, and special-purpose modules in a compact form factor.

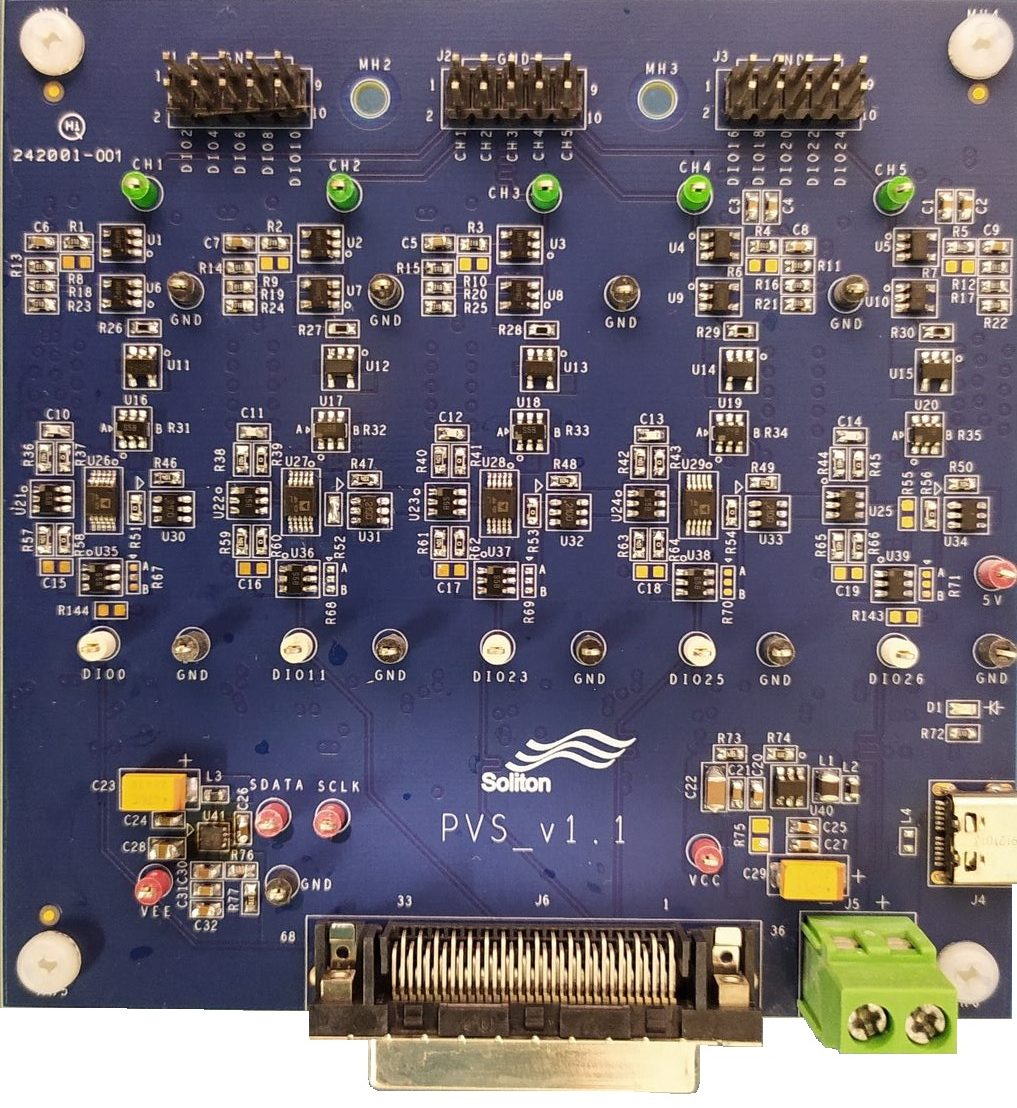

What is the interposer board referenced in the system diagram?

The Protocol Validation Suite requires custom external circuitry for signal conditioning. Each purchase comes with a complimentary interposer board, which is a separate PCB designed and delivered by us.

Which oscilloscope models are supported?

The Protocol Validation Suite supports any NI scope by default. The tool has a flexible architecture that allows the support of other oscilloscope models. We can help you in building the oscilloscope plugin for one of your oscilloscopes

What type of documentation and training will be available for each solution?

User manuals, Getting started guides, and tutorial videos are available for each solution and can be easily accessed from within the product. Additionally, we will provide short live training sessions upon request.

Can the tool be used for out-of-the-box validation?

Yes, The tool comes with out of box test scripts which can be used for validation after entering the device-specific details

Why was I3C Master- I3C Slave terms are renamed to I3C Controller – I3C Target?

As a part of terminology replacement efforts within MIPI Alliance, MIPI Alliance has deprecated the Master-Slave terminologies and replaced them with Controller-Target terminologies.

Technical Documentation

Soliton’s I3C Validation Suite is an off-the-shelf validation tool using NI’s PXI platform, which helps to validate the devices’ compliance with the timing and electrical specifications of the MIPI I3C® protocol. It contains the below components.

- NI PXIe 657x – Digital Pattern Generation Card with the PXIe Chassis setup

- Soliton PVS Interposer Board

- Oscilloscope – For performing voltage measurements

- Soliton I3C Validation Suite Software compatible with Windows OS (Win 10)

For more details, download the datasheet.

Download Datasheet - I3C Protocol Validation Suite Specifications

Download Datasheet - I3C Protocol Validation Suite Specifications

Download Datasheet - I3C Protocol Validation Suite Specifications

Please enter your details, you will receive an immediate automated email with our I3C Protocol Validation Suite Datasheet.

Hardware

Soliton’s I3C Validation suite is based on the NI – PXI Platform and the NI part configuration lists the hardware required to perform the validation

The solution also needs a custom Interposer Board for signal conditioning purposes.

Support & Training

For any queries, contact us at [email protected]. We will respond within 1 Business day.

TYPICAL USER BASE FOR I3C VALIDATION SUITE

- Design Engineers, Test Engineers, Post Silicon Validation Engineers, Engineering Managers, Validation Managers, Lab Managers, etc from the Semiconductor Industry

- Post Silicon validation of Chips with I3C interface

- Semiconductor Chip Manufacturers making I3C Devices

- Conformance Test Suite (CTS) for I3C devices

- Companies making Sensors/chips used for IoT, Mobile Ecosystems like smartphones, wearables, etc., and Automotive ecosystems. These companies need to adhere to and test against the MIPI I3C® specification

- Companies making devices that need to adhere to and test against the JESD82-511, JESD301-1, JESD302-1, JESD300-5 and JESD303-1 specification standards which includes specs for the I3C interface. (PMIC 5000, PMIC 5010, PMIC 5100, DDR5, TS511x)

OTHER PROTOCOL VALIDATION SERVICES OFFERED BY SOLITON

I2C Protocol Validation ![]() SPI Protocol Validation

SPI Protocol Validation ![]() SPMI Protocol Validation

SPMI Protocol Validation ![]() RFFE Protocol Validation

RFFE Protocol Validation ![]()

UART Protocol Validation ![]() SMBus Protocol Validation

SMBus Protocol Validation ![]() PMBus Protocol Validation

PMBus Protocol Validation ![]()

Demo Request Form

Please fill in the following form and we shall get in touch with you soon to set up a demo of the requested service/product. Thank you!

Error: Contact form not found.

DOWNLOAD NOW

Fill in this form and submit for your download to start automatically

Error: Contact form not found.

Download PRIM Brochure

Submit this form and the PRIM Brochure document will be sent to your email.

Error: Contact form not found.