Customer’s Requirement with Stress Testing and Glitch Injection

utilized a validation system called the Data Timing Generator (DTG) for their I2C and I3C protocol testing. This system helped them achieve the functional and basic timing tests. However, the customer relied on writing manual test scripts in Python, which required looking up documentation for functions compatible with their tool. This took extensive manual effort.

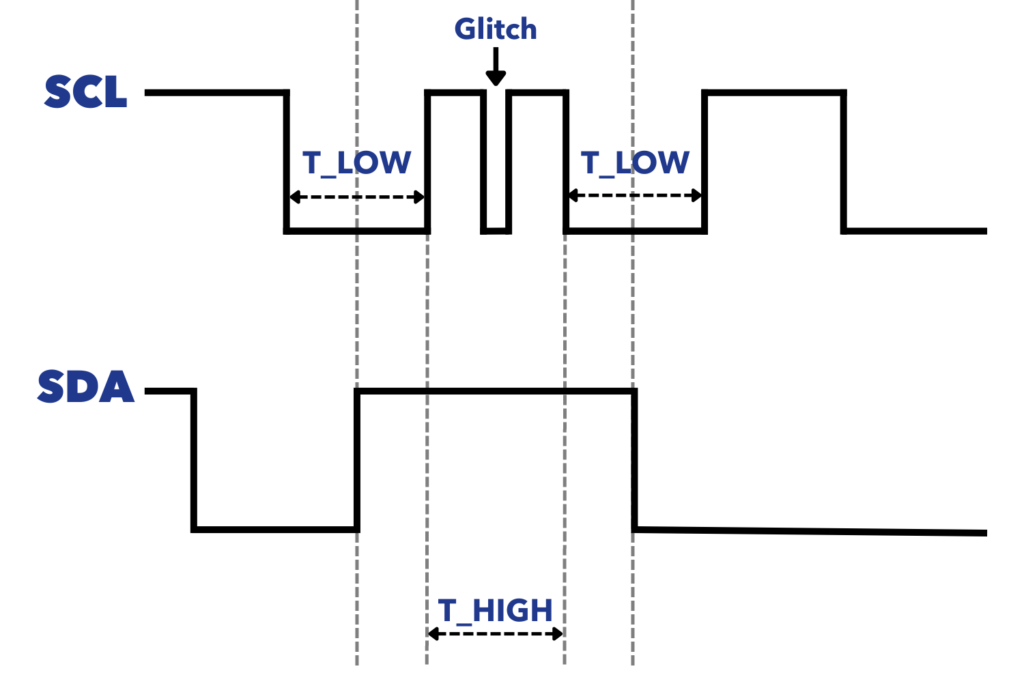

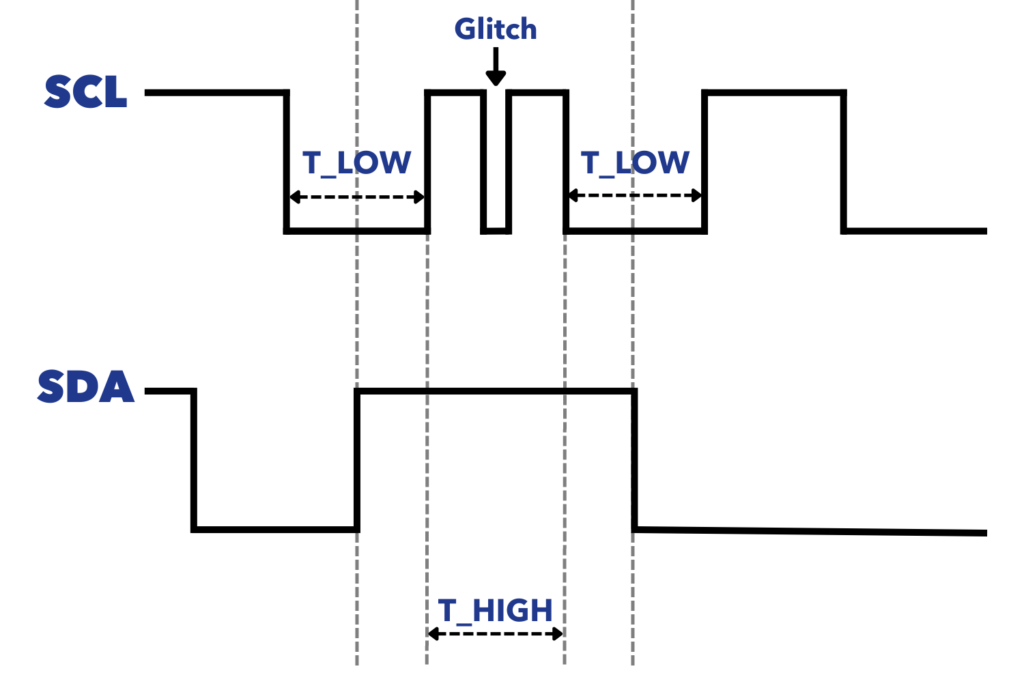

In addition to the basic tests, the customer had two particular test cases to validate their device. One test case was to verify how well the device performed while handling high-volume transactions (known as the stress test), and the other was to examine how tolerant the device was to glitches in the I2C and I3C signals (glitch injection).

-

Handling High-Volume Transactions for Performance Validation

Stress testing involves rapidly executing numerous read or write operations (or both) to a register or a bank of registers to ensure robust device performance. As part of the stress test, our customer needed to perform more than 1,00,000 transactions on their DUT, to ensure that the DUT responds accurately to all the transactions.

While their existing setup could handle the task, the process was highly time-consuming, taking over an hour to complete. The customer wanted a mechanism to perform this test quickly and infer the test results through a report or GUI that could analyze the response for each iteration.

In addition to the stress test, the customer wanted to test their DUT’s performance against glitches in the SCL/SDA signals. They wanted to induce glitches at various places of SCL and SDA lines, with varying widths of the glitch, and verify the device’s tolerance to these glitches.