Customer’s Hurdles with the Existing Workflow

Analyses of semiconductor chip packaging involve advanced simulation concepts across multiple applications, running for extended durations and yielding complex results. This process, combined with the steep learning curve of simulation applications, posed challenges for our customer, a prominent semiconductor entity. They were utilizing a 3D modeling application that enabled their R&D engineers to perform mechanical analysis during pre-silicon validation.

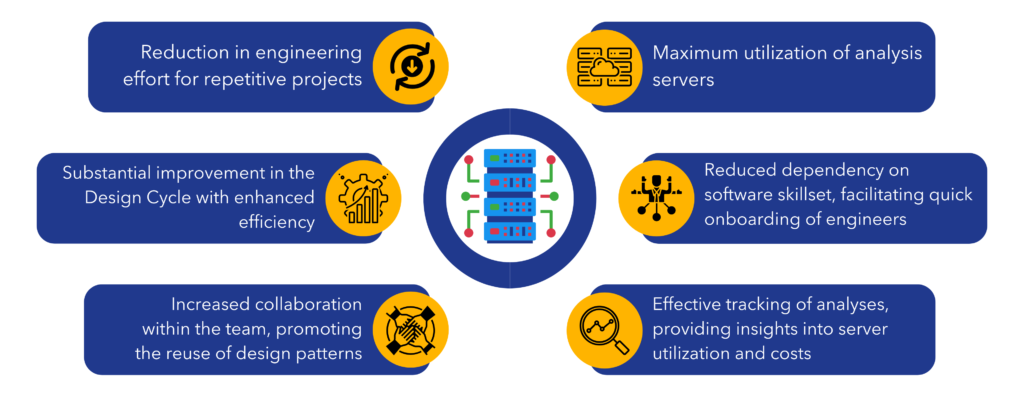

They were looking to enhance their overall workflow by automating their manual processes and by organizing the artifacts modularly, in order to improve their operational efficiency. Their current process entailed some setbacks that prompted considerations for improvement in the workflow, which required:

- Streamlining the application interface to minimize the learning curve, lessen dependency on specific software skills for test development, and enable users to perform validation effortlessly.

- Implementing comprehensive workflow automation to minimize manual intervention, improving overall efficiency.

- Enhancing simulation server utilization to expedite test completion and reduce overall processing time.

- Organization of workflow artifacts for efficient reuse of design, configuration, and execution files, enabling data retrieval and reuse.

- Addressing inefficiencies across package configuration, assembly setup, and analysis configuration stages.

- Resolving the procedural guideline ambiguities to streamline result generation.

Recognizing the areas for improvement in their existing workflow, the customer actively sought a reliable partner to refine, simplify, and streamline the process, thereby prompting a collaboration with Soliton.